在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1282

1282

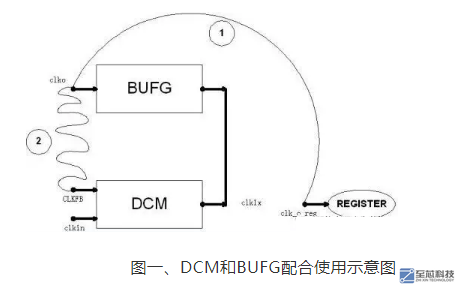

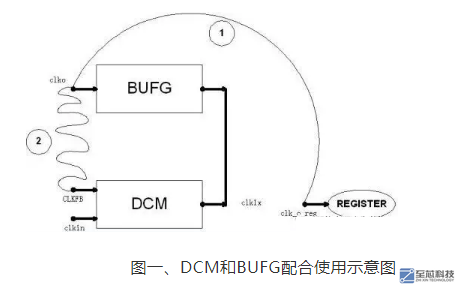

赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19749

19749

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12245

12245

SERDES恢复出的数据进入FPGA有一个解复用和时钟域转换的问题,Stratix GX包含了专用电路可以完成8/10bit数据到8/10/20bit数据的Mux/Demux,另外SERDES收端到FPGA内部通用逻辑资源之间还有FIFO可以完成数据接口同步,其电路结构如图所示。

2018-04-08 08:46:50 9476

9476 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

2019-09-10 15:12:31 6418

6418

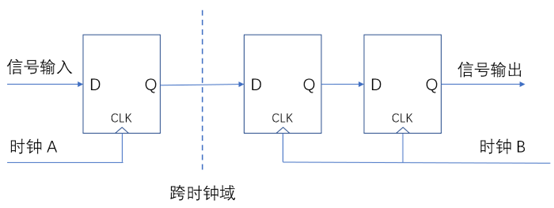

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2020-11-21 11:13:01 3340

3340

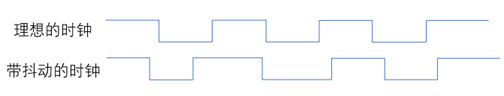

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期

2020-11-23 13:08:24 3602

3602

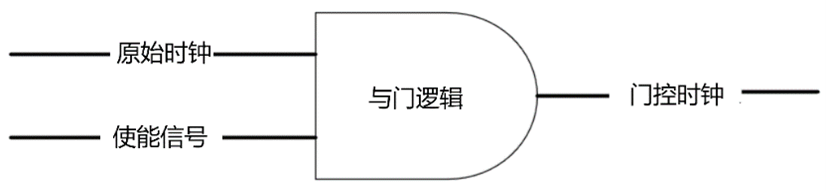

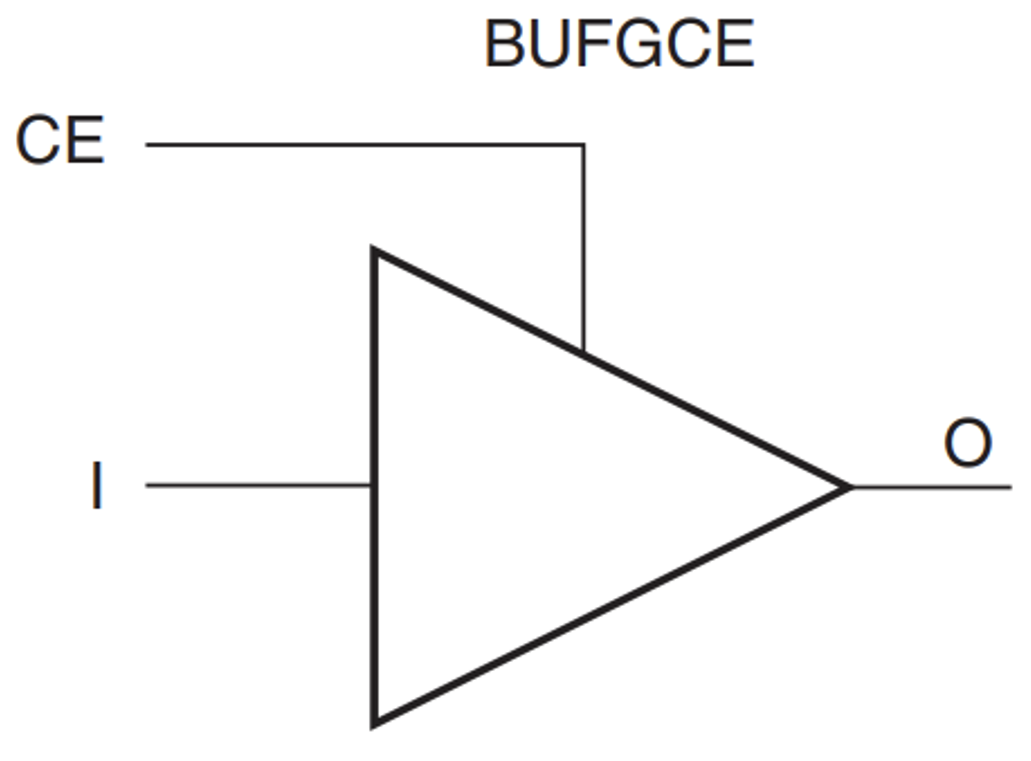

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 4892

4892

当我刚开始我的FPGA设计生涯时,我对明显更小、更不灵活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常简单的时钟规则之一是尽可能只使用单个时钟。当然,这并不总是可能的,但即便如此,时钟的数量仍然有限。

2022-09-30 08:49:26 1378

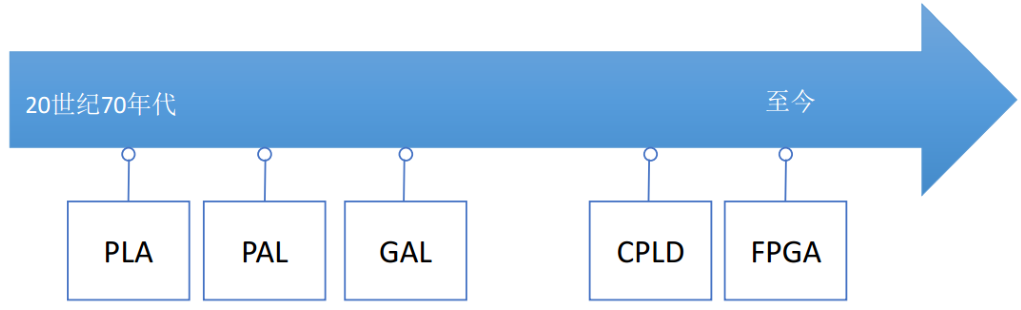

1378 每一个系列的FPGA都有其相应的内部结构),FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

2022-10-25 09:01:05 1841

1841 在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1425

1425 。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 709

709

,以满足各种设计需求,并提供时钟驱动逻辑资源的灵活性和可扩展性。那今天我们一起解剖Xilinx 7系列FPGA的时钟结构,看看它到底如何实现如此丰富的时钟资源并能够做到完美平衡。

2023-08-31 10:44:31 1262

1262

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 2396

2396

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 589

589

FPGA 在通信领域的应用可以说是无所不能,得益于 FPGA 内部结构的特点,它可以很容易地实现分布式的算法结构,这一点对于实现无线通信中的高速数字信号处理十分有利。

2024-01-24 13:46:33 499

499

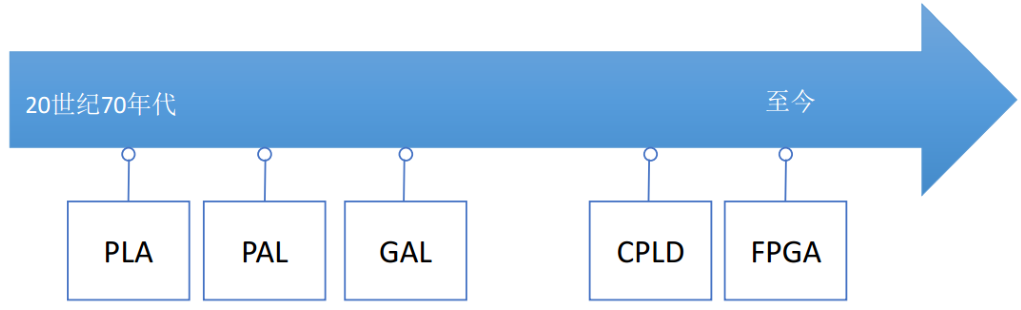

(08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2022-02-23 07:26:05

(12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:08:36

(30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2022-02-23 06:32:02

(29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2022-02-23 07:27:45

本帖最后由 rousong1989 于 2015-1-27 11:45 编辑

FPGA入门:内里本质探索——器件结构本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门

2015-01-27 11:43:10

时钟电路本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 人体拥有非常奇妙的循环系统,而心脏是这个循环系统

2019-04-12 01:15:50

,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主 要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌

2017-05-09 15:10:02

时钟电路本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 人体拥有非常奇妙的循环系统,而心脏是这个循环系统

2015-04-08 10:52:10

FPGA时钟和复位电路设计本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt FPGA的时钟输入都有专用引脚

2015-04-24 08:17:00

FPGA实现逻辑函数用的什么电路结构?

2017-01-01 21:49:23

存储结构。 4.丰富的布线资源 布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。布线资源的划分: 1)全局性的专用布线资源:以完成器件内部的全局时钟

2019-09-24 11:54:53

存储结构。 4.丰富的布线资源 布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。布线资源的划分: 1)全局性的专用布线资源:以完成器件内部的全局时钟

2016-08-23 10:33:54

存储结构。 4.丰富的布线资源 布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。布线资源的划分: 1)全局性的专用布线资源:以完成器件内部的全局时钟

2016-09-18 11:15:11

存储结构。 4.丰富的布线资源 布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。布线资源的划分: 1)全局性的专用布线资源:以完成器件内部的全局时钟

2016-10-08 14:43:50

存储结构。 4.丰富的布线资源 布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。布线资源的划分: 1)全局性的专用布线资源:以完成器件内部的全局时钟和全局

2016-07-16 15:32:39

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

个主振荡器开始,经过多次的倍频、分频、锁相环等电路,生成每个模块的独立时钟信号。相应的从主振荡器到各个模块的时钟信号通路也称为时钟树。stm32时钟树结构如下:时钟系统概述①、HSI 是高速内部时钟

2022-01-11 07:31:55

FPGA的同步电路设计基础知识 同步电路设计将系统的状态变化与时钟信号同步,通过这种方法降低电路设计难度。一、触发器定义:一种储存1个二进制位的存储单元,可以用做时序逻辑电路的记忆元件。FPGA逻辑

2019-12-11 15:02:36

`例说FPGA连载17:时钟与复位电路设计特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc FPGA的时钟输入都有专用引脚,通过这些专用

2016-08-08 17:31:40

的问题是,我可以在FPGA内部使用这个时钟作为FPGA和电路板的主时钟吗?我有一个应用程序,我想在板上尽可能少的部件,我不关心主时钟频率是什么,只要它是1-50MHz时钟。要使用CCLK我必须有一个PCB

2019-05-07 13:40:54

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

视频过大,打包成8个压缩包基于FPGA设计的数字时钟.part01.rar (20 MB )基于FPGA设计的数字时钟.part02.rar (20 MB )基于FPGA设计的数字时钟

2019-05-14 06:35:34

时间对 FPGA 的内部结构产生了一定的兴趣,所以找来了一本书看,这篇博客相当于是对其中相关知识点的梳理与总结, 前置知识是数字电路逻辑 。参考书目写在了下面:

FPGA 原理和结构:这本书是日本可重构

2024-04-03 17:39:53

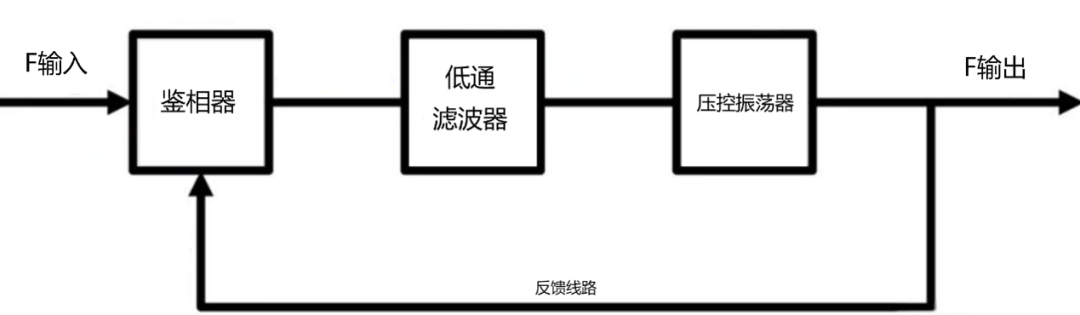

信号与输入数据之间的相位关系,使其同步。 传统的基于FPGA的时钟恢复电路的结构如图1所示。如前所述,这种结构的电路用中低端FPGA,工作

2009-10-24 08:38:08

主要讲解了fpga设计、方法和实现。这本书略去了不太必要的理论、推测未来的技术、过时工艺的细节,用简明、扼要的方式描述fpga中的关键技术。主要内容包括:设计速度高、体积小、功耗低的体系结构方法

2012-03-01 14:59:23

在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 45

45 一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 影响FPGA设计中时钟因素的探讨:时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时

2009-11-01 14:58:33 26

26 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 提出了一种基于FPGA的时钟跟踪环路的设计方案,该方案简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方案能够使接收机时钟快速准确地跟踪发

2010-11-19 14:46:54 31

31 摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1250

1250

基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 3696

3696

大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 653

653

FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的

2010-09-10 17:25:27 2187

2187 本文将探讨FPGA时钟分配控制方面的挑战,协助开发团队改变他们的设计方法,并针对正在考虑如何通过缩小其时钟分配网络的规模来拥有更多的FPGA I/O,或提高时钟网络性能的设计者们

2011-03-30 17:16:32 942

942

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3504

3504

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 179

179 FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1127

1127

电源、时钟和复位电路图(Altera FPGA开发板)如图所示:

2012-08-15 14:42:33 9418

9418

DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 基于FPGA的数字时钟设计,可实现闹钟的功能,可校时。

2016-06-23 17:15:59 64

64 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 适于数据通路电路的FPGA结构

2017-01-18 20:39:13 5

5 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4309

4309 介绍一种采用FPGA(现场可编程门阵列电路)实现SDH(同步数字体系)设备时钟芯片设计技术,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该技术,可以在FPGA 中实现需要专用芯片才能实现的时钟芯片各种功能,而且输入时钟数量对比专用芯片更加灵活,实现该功能的成本降低三分之一.

2017-11-21 09:59:00 1864

1864

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 9004

9004

提出了一种基于FPGA的时钟跟踪环路的设计方粢,该方粢简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方集能够使接收机时钟快速准确地跟踪发射机时钟的变化,且时钟抖动小、稳准度高、工作稳定可靠。

2017-11-30 15:10:20 5

5 时钟是数字电路中所有信号的参考,特别是在FPGA中,时钟是时序电路的动力,是血液,是核心。

2018-03-28 17:12:20 13237

13237 有些FPGA学习者,看Xilinx的Datasheet会注意到Xilinx的FPGA没有PLL,其实DCM就是时钟管理单元。 1、DCM概述 DCM内部是DLL(Delay Lock Loop结构

2018-05-25 15:43:53 7932

7932

FPGA 器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。

2019-12-26 07:09:00 1668

1668 跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 2930

2930 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 5141

5141

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2590

2590 简单介绍了FPGA器件的发展及基本结构、设计方法,并以PWM电路的FPGA实现为例,说明了FPGA在电力系统中的应用前景.

2020-10-20 16:16:50 11

11 对于 FPGA 来说,要尽可能避免异步设计,尽可能采用同步设计。 同步设计的第一个关键,也是关键中的关键,就是时钟树。 一个糟糕的时钟树,对 FPGA 设计来说,是一场无法弥补的灾难,是一个没有打好地基的楼,崩溃是必然的。

2020-11-11 09:45:54 3701

3701 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们

2021-03-22 10:09:58 11805

11805

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4428

4428 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 (08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1513

1513 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2716

2716 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 704

704

“时钟是时序电路的控制者”这句话太经典了,可以说是FPGA设计的圣言。FPGA的设计主要是以时序电路为主,因为组合逻辑电路再怎么复杂也变不出太多花样,理解起来也不没太多困难。

2022-12-02 09:53:11 492

492 跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

2023-05-25 15:06:00 1233

1233

FPGA多bit跨时钟域适合将计数器信号转换为格雷码。

2023-05-25 15:21:31 2032

2032

时钟是整个FPGA设计里面无法回避的事物,不能认识时钟也就没法做FPGA设计。

2023-06-28 11:00:58 244

244

常见的FPGA核心电路可以归纳为五个部分:电源电路、时钟电路、复位电路、配置电路和外设电路。下面将对各部分电路进行介绍。

2023-07-20 09:08:31 528

528 基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0 域时,由于时钟频率不同,所以可能会产生元件的不稳定情况,导致传输数据的错误。此时我们需要采取一些特殊的措施,来保证跨时钟域传输的正确性。 FPGA跨时钟域通信的基本实现方法是通过FPGA内部专门的逻辑元件进行数据传输。发送方用一个逻辑电路

2023-10-18 15:23:51 645

645 设计都涉及到对RAM的读写操作。在FPGA芯片中,RAM也叫做存储块(Block RAM),可以存储大量的数据。 FPGA中的RAM可以一次读取多个数据,这是因为RAM的结构是一个多列的数据表格,其中每一列都是一个包含多个存储单元的块。通过在时钟的一次上升沿来读取RAM中的数据,这个操作必须在一个

2023-10-18 15:28:20 705

705 FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢? FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据不同需要编程,实现不同的功能。在FPGA

2023-10-25 15:14:20 1150

1150 今天来聊一聊时钟树。首先我先讲一下我所理解的时钟树是什么,然后介绍两种时钟树结构。

2023-12-06 15:23:47 615

615 FPGA输入的时钟信号必须是方波么?正弦波会有影响么? FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大

2024-01-31 11:31:42 1514

1514

电子发烧友App

电子发烧友App

评论