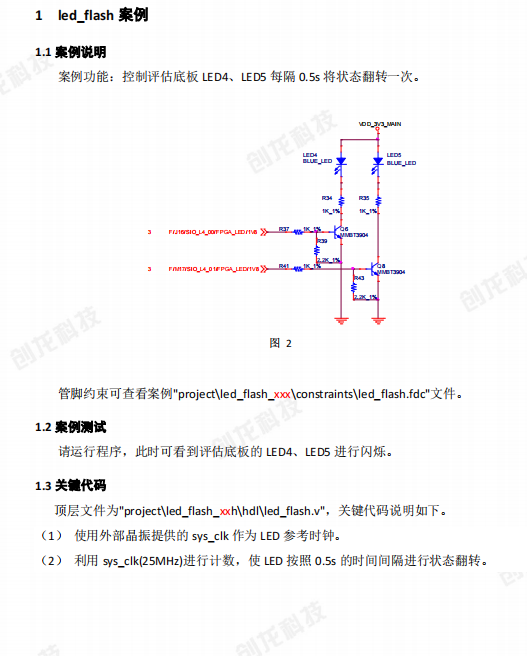

可编程逻辑

基于自研芯片+顶级AMD FPGA,西门子EDA发布“快而全”的Veloce CS

电子发烧友网报道(文/吴子鹏)在大型芯片设计过程中,验证被认为是整体流程中最复杂、最耗时的环节之一。有数据显示,目前功能验证约占整个芯片开发过程投入的60%-70%,是芯片项目能否...

国产FPGA应用专题--易灵思Efinity软件使用心得

做为FPGA的集成开发环境,不同的厂家其实大同小异。很多国产厂家,如安路,高云,会在软件上贴近Xilinx和Intel,以节省客户的软件使用成本。而国产厂商的易灵思的集成开发环境Efinity似乎并...

易灵思RAM使用--Update4

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径 在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。 (1)如果文件放在工程目...

gtkwave界面每次都更新太麻烦?来个小技巧-v1

迄今为止,大家都在吐槽gtkwave debug每次弹窗都会覆盖上一次弹窗设置好的排序和参数。下面我们分享一个可以暂时规避该问题的方法,聊以慰藉久被摧残的心~~。 (1)添加debug ,无论手动或者自...

易灵思Jtag_bridge_loader生成-v2

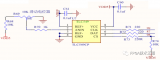

Efinity版本:2023.1及以前版本。 易灵思器通过jtag bridge烧写flash时需要自己生成一个jtage birdge文件。jtage bridge 工程的目的是为了打通JTAG与flash的连接。 (1)打开IPM (2)选择Memory Controllers --> J...

FPGA入门必备:Testbench仿真文件编写实例详解

在编写完HDL代码后,往往需要通过仿真软件Modelsim或者Vivadao自带的仿真功能对HDL代码功能进行验证,此时我们需要编写Testbench文件对HDL功能进行测试验证。...

FPGA工程的时序约束实践案例

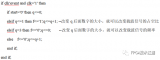

详细的原时钟时序、数据路径时序、目标时钟时序的各延迟数据如下图所示。值得注意的是数据路径信息,其中包括Tco延迟和布线延迟,各级累加之后得到总的延迟时间。...

Xilinx FPGA的约束设置基础

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。...

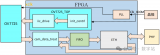

基于FPGA的光纤通信加密系统

FPGA 设计加密算法具有安全性高,加密速度快,开发周期短,开发成本较低, 可重配,可靠性高以及移植性好等优点。 系统链路部分采用 Aurora 协议,该协议是一款轻量级的光纤链路协议,具有...

基于FPGA设计的BRAM内部结构

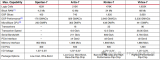

再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。...

FPGA技术的五大优势

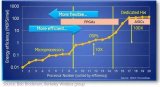

各行各业纷纷采用FPGA芯片是源于FPGA融合了ASIC和基于处理器的系统的最大优势。 FPGA能够提供硬件定时的速度和稳定性,且无需类似自定制ASIC设计的巨额前期费用的大规模投入。...

基于FPGA技术的手势识别控制型多功能机械臂系统

首先通过图像采集设备来获取手势图像,通过手势建模将获取的手势图像用数学模型描述出来,最后根据得到的手势识别所需要的模型参量判别出具体的手势形态。...

基于FPGA技术的智能驾驶辅助系统设计方案

图像的采集使用的是 NUOXI ZL-008 型号USB 摄像头,该摄像头支持分辨率640*480,帧率 30 帧/秒,增强像素数1200 万,可以满足本文研究中对 图像的清晰度和实时性的要求。...

FPGA通过AXI总线读写DDR3实现方式

AXI总线由一些核心组成,包括AXI主处理器接口(AXI4)、AXI处理器到协处理器接口(AXI4-Lite)、AXI主外设接口(AXI4)、AXI外设到主处理器接口(AXI4-Lite)等。...

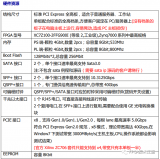

基于FPGA的多通道高速信号采集与处理平台设计方案

以核心处理板为核心,由信号源产生的待处理模拟信号通过同轴线缆连接到核心处理板的信号接口,同时,连接同步时钟等其他相关信号到核心处理板。...