可编程逻辑

快速开箱即用体验 AMD / Xilinx Kria™ KD240驱动器入门套件

快速开箱即用体验 AMD / Xilinx Kria™ KD240驱动器入门套件...

作为嵌入式系统核心,FPGA如何从产品和系统侧赋能创新?

电子发烧友网报道(文/吴子鹏)根据《2023-2028年中国FPGA芯片行业发展前景预测及投资战略咨询报告》,2022年全球FPGA市场规模为79.4亿美元,2023年增长至93.6亿美元,从2016年到2023年的年复合增长...

易灵思的时钟网络问题

在T20中有16个全局时钟网络GCLK。在芯片的左右两侧各8个。全局时钟管脚或者PLL的输出时钟通过左右两个CLKMUX上全局网络。左侧的PLL(包括PLL_TL0和PLL_TL1)上左侧的CLKMUX_L;右侧的PLL(包括PLL_TR0,PL...

基于安路科技FPSoC器件DR1系列的视频采集/显示/处理解决方案

安路科技全新一代FPSoC器件DR1系列, 集成高性能硬核处理器双核ARM Cortex-A35或单核64位RISC-V、丰富的片上内存和高低速外设接口、FPGA可编程逻辑、NPU/JPU硬件加速单元, 内部通过高带宽总线互联...

FPGA厂商紫光同创入选多样性算力产业及标准推进委员会黄金成员

日前,“共筑新算力,智启新未来”多样性算力产业峰会2024在北京成功举办。本次峰会由中国通信标准化协会多样性算力产业及标准推进委员会主办,来自计算产业代表近400人参加。紫光同创...

微芯将为韩国航天产业提供抗辐射的FPGA和MCU设备

近日于位于首尔南方水原市举行的ASSIC 2024研讨会上,我们广泛宣传了我们所研发的抗辐射FPGA与微控制器(MCU)设备,致力于为当前迅速崛起的韩国航天产业提供具有抗辐射特性的先进半导体技...

加法进位链的手动约束

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。 在outflow下会生成一个.qplace文件 。用于指示布线的各个原语资源的分布位置 。 它的内容主是 是原语的单元名...

FPGA是实现敏捷、安全的工业4.0发展的关键

到2028年,全球工业4.0市场规模预计将超过2790亿美元,复合年增长率为16.3%。虽然开发商和制造商对这种高速增长已经习以为常,但其影响才刚刚开始显现。通过结合云计算、物联网(IoT)和人...

Altera将AI注入新的中端FPGA

今年2月,英特尔宣布将Altera分拆为一家专注于FGPA的独立公司。拥有40年的血统,Altera的名字在业界肯定是众所周知的。虽然该公司仍由英特尔100%控股,但Altera的首席执行官Sandra里维拉表示,英...

FPGA入门必备:Testbench仿真文件编写实例详解

在编写完HDL代码后,往往需要通过仿真软件Modelsim或者Vivadao自带的仿真功能对HDL代码功能进行验证,此时我们需要编写Testbench文件对HDL功能进行测试验证。...

FPGA工程的时序约束实践案例

详细的原时钟时序、数据路径时序、目标时钟时序的各延迟数据如下图所示。值得注意的是数据路径信息,其中包括Tco延迟和布线延迟,各级累加之后得到总的延迟时间。...

Ti60F100 内外flash操作方案

有客户认为Ti60F100内部flash容量比较小,只有16Mb,需要外挂flash.这里我们提供了内部flash和外部flash分别操作的方案。 该程序是通过SOC操作4线的外部flash和内部flash.程序先经过外部flash的擦除,写...

2024-05-20标签:FlaSh695

Xilinx FPGA的约束设置基础

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。...

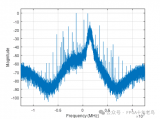

基于FPGA的光纤通信加密系统

FPGA 设计加密算法具有安全性高,加密速度快,开发周期短,开发成本较低, 可重配,可靠性高以及移植性好等优点。 系统链路部分采用 Aurora 协议,该协议是一款轻量级的光纤链路协议,具有...

基于自研芯片+顶级AMD FPGA,西门子EDA发布“快而全”的Veloce CS

电子发烧友网报道(文/吴子鹏)在大型芯片设计过程中,验证被认为是整体流程中最复杂、最耗时的环节之一。有数据显示,目前功能验证约占整个芯片开发过程投入的60%-70%,是芯片项目能否...

基于FPGA设计的BRAM内部结构

再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。...