微芯将为韩国航天产业提供抗辐射的FPGA和MCU设备

近日于位于首尔南方水原市举行的ASSIC 2024研讨会上,我们广泛宣传了我们所研发的抗辐射FPGA与微控制器(MCU)设备,致力于为当前迅速崛起的韩国航天产业提供具有抗辐射特性的先进半导体技术。

- 专栏要长高

- 4天前

- 235

- 0

- 0

原FPGA产业发展的三大特色和趋势,国产FPGA厂商有怎样的机遇和挑战

电子发烧友网报道(文/吴子鹏)统计数据显示,2022年全球FPGA市场规模为79.4亿美元,2023年成长为93.6亿美元,2016-2023这几年的年复合增长率达10.1%。FPGA是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物,具有硬件可重构的体系结构,其数字电路可以通过编程的方式在芯片出厂后重新构造,具有并行性、低延时性和灵活性等特性,应用领域非常广泛。 近日,赛迪顾问股份有限公司集成电路中心主任腾冉表示,全球

- 专栏Felix分析

- 7天前

- 1997

- 0

- 1

在FPGA中利用IP核实现I/Q信号的产生

对于有些通信类,光通信类以及射频方向的同学都知道在通信的信号处理中,输入的信号需要分成两路(I路和Q路),也被称作为正交调制信号。

- 专栏FPGA技术江湖

- 10天前

- 301

- 0

- 0

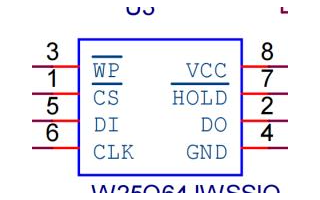

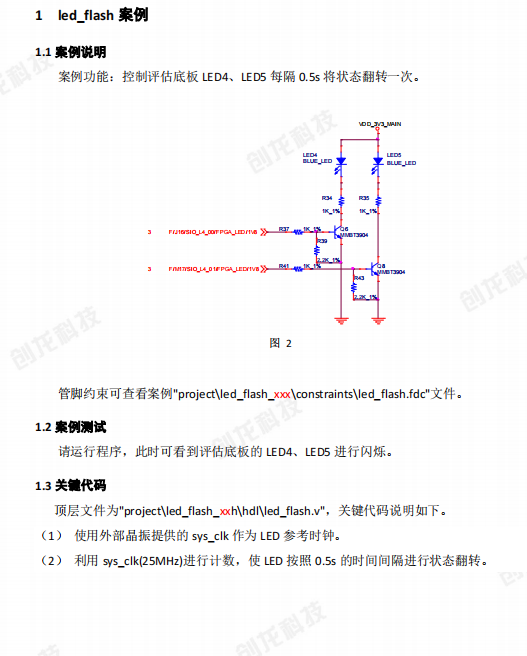

Ti60F100 内外flash操作方案

有客户认为Ti60F100内部flash容量比较小,只有16Mb,需要外挂flash.这里我们提供了内部flash和外部flash分别操作的方案。 该程序是通过SOC操作4线的外部flash和内部flash.程序先经过外部flash的擦除,写入和读出操作,再经过外部flash的擦除,写入和读出操作,每次读出后会进行数据的比较以判断写入和读出的数据是否一致。 硬件方案如下: 由于使用的RSICV是softjtag操作,所以使用了两个下载器。在硬件设计外外挂一片64Mb的flash。 外部flash管脚分配 flash管脚 FPG

- 专栏XL FPGA技术交流

- 18天前

- 505

- 0

- 0

原加法进位链的手动约束

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。 在outflow下会生成一个.qplace文件 。用于指示布线的各个原语资源的分布位置 。 它的内容主是 是原语的单元名 表示水平位置,对应floorplan. 表示垂直位置 , 对应f loorplan . 表示子块的位置 。目前只DSP24和DSP12可以有子块。在一个block可以指定多个字块。 是给block的一个编号,从0开始往下排。 锁定过程如下: stp1:并把outflow下面的.qplace文件得到到工程目录下(可以修改名字也可

- 专栏XL FPGA技术交流

- 18天前

- 560

- 0

- 0

基于FPGA的AES256光纤加密设计案例实现

近年来,信息安全应用于生活中的各个领域.在光通信系统中,往往对速率有着较高的追求。其中对光模块,光纤通信中的传输算法,传输的模式以及光波段选取有密切关联。

- 专栏FPGA技术江湖

- 28天前

- 779

- 0

- 1

Altera将AI注入新的中端FPGA

今年2月,英特尔宣布将Altera分拆为一家专注于FGPA的独立公司。拥有40年的血统,Altera的名字在业界肯定是众所周知的。虽然该公司仍由英特尔100%控股,但Altera的首席执行官Sandra里维拉表示,英特尔计划在今年晚些时候出售部分股份,并在大约两年内进行IPO。 All About Circuits 在嵌入式世界大会上,Altera发布了几项公告,包括: 全新Agilex 5 SoC FPGA Quartus Prime设计软件更新 FPGA生命周期支持扩展 全新Agilex 5 SoC FPGA 随着中档Agilex 5的发布,Altera声称这是第一个在

- 专栏eeDesign

- 1月前

- 974

- 0

- 0

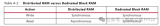

基于FPGA BRAM的多端口地址查找表与FPGA BRAM的资源分析

在多端口交换机的设计中,交换机的每个端口都会各自维护一张查找表,数据帧进入到交换机后,需要进行查表和转发。

- 专栏网络交换FPGA

- 1月前

- 628

- 0

- 0

Xilinx FPGA BGA推荐设计规则和策略(二)

工程师必须在设计阶段早期评估功率需求,以确保有足够的层和面积为需要功率的BGA焊盘提供足够的功率。

- 专栏FPGA技术实战

- 1月前

- 428

- 0

- 0

时序约束实操

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自己的SDC文件添加到工程)。

- 专栏XL FPGA技术交流

- 1月前

- 1272

- 0

- 0

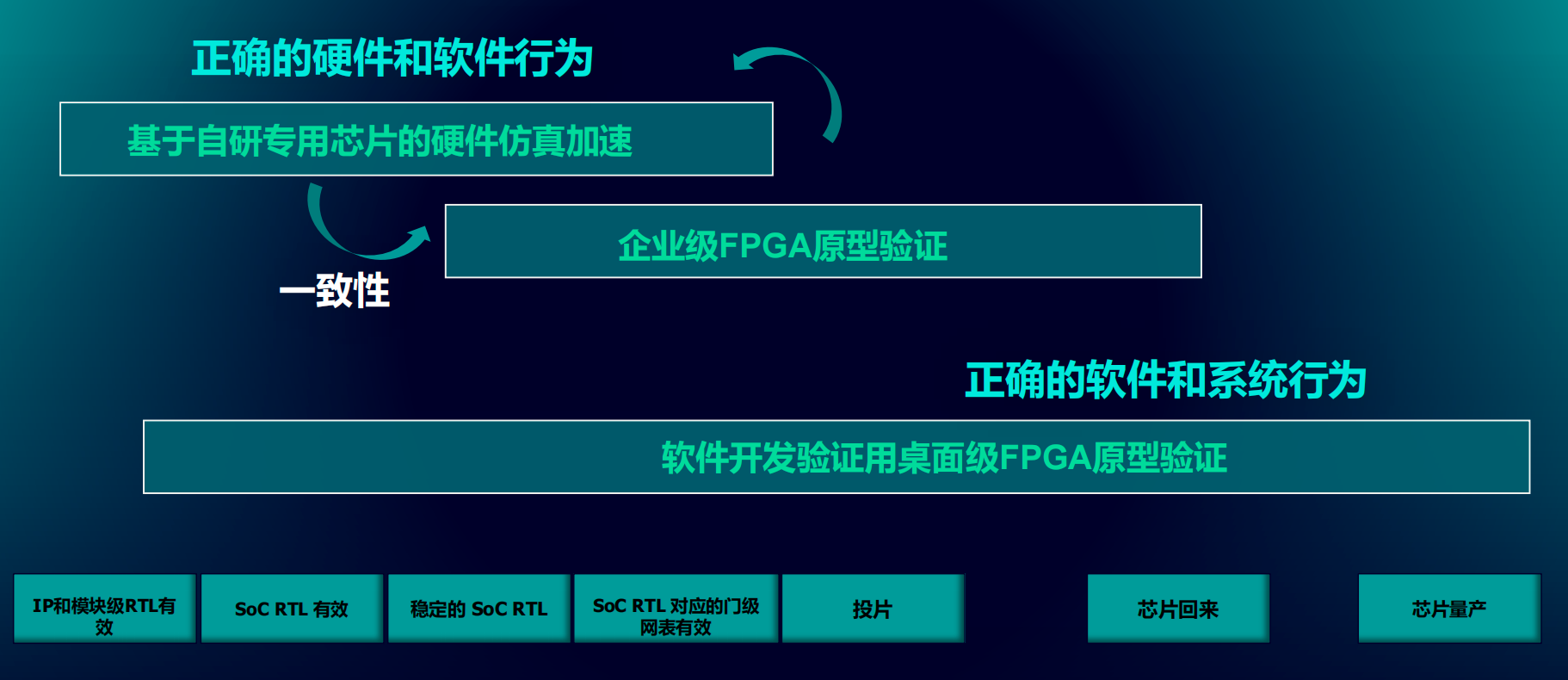

原基于自研芯片+顶级AMD FPGA,西门子EDA发布“快而全”的Veloce CS

电子发烧友网报道(文/吴子鹏)在大型芯片设计过程中,验证被认为是整体流程中最复杂、最耗时的环节之一。有数据显示,目前功能验证约占整个芯片开发过程投入的60%-70%,是芯片项目能否成功落地的关键。 随着芯片规模越来越大,复杂度日益提升,芯片验证对于平台的要求也越来越高。为了帮助芯片设计和验证工程师更好地应对这一挑战,西门子数字化工业软件推出Veloce CS硬件辅助验证和确认系统。 西门子EDA硬件辅助验证产品管理高级总监

- 专栏Felix分析

- 1月前

- 2786

- 0

- 1

国产FPGA应用专题--易灵思Efinity软件使用心得

做为FPGA的集成开发环境,不同的厂家其实大同小异。很多国产厂家,如安路,高云,会在软件上贴近Xilinx和Intel,以节省客户的软件使用成本。而国产厂商的易灵思的集成开发环境Efinity似乎并不像大厂,显得差异更大一些。但经过一段时间的使用,我个人认为并不需要因为差异大些就过于排斥,Efinity在使用上并不会麻烦。 接下来我们来聊一下Efinity的一些功能及个人使用感受。主要包括以下几个方面: (1)软件安装; (2)软件界面; (3)控制面板;

- 专栏XL FPGA技术交流

- 1月前

- 739

- 0

- 0

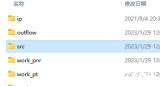

易灵思RAM使用--Update4

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径 在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。 (1)如果文件放在工程目录下,写法如下: .RAM_INIT_FILE("./ram_init_file.inithex" ) 或者.RAM_INIT_FILE("ram_init_file.inithex" ) (2)如在工程目录下新建一个src文件。写法如下: .RAM_INIT_FILE("./src/ram_int_file.mem") 2.初始化文件格式 初始化文件 支持.inithex和.mem.都是按顺序以16进制输入数据即可。

- 专栏XL FPGA技术交流

- 1月前

- 564

- 0

- 0

为什么使用FPGA?FPGA为什么比GPU的延迟低这么多?

众所周知,通用处理器(CPU)的摩尔定律已入暮年,而机器学习和 Web 服务的规模却在指数级增长。

- 专栏FPGA设计论坛

- 1月前

- 943

- 0

- 2

原gtkwave界面每次都更新太麻烦?来个小技巧-v1

迄今为止,大家都在吐槽gtkwave debug每次弹窗都会覆盖上一次弹窗设置好的排序和参数。下面我们分享一个可以暂时规避该问题的方法,聊以慰藉久被摧残的心~~。 (1)添加debug ,无论手动或者自动都可以。这里为简便就通过Wizard来添加。 (2)编译程序,连接debug运行。会弹出抓信号的窗口,我们这里称为 弹出窗。要说明的是如果在环境变量中没有添加gtkwave环境变量是不会有弹出窗的。 (3)这时在工程目录下,根据要抓取信号的core name在工程目录下

- 专栏XL FPGA技术交流

- 1月前

- 732

- 0

- 0

原易灵思Jtag_bridge_loader生成-v2

Efinity版本:2023.1及以前版本。 易灵思器通过jtag bridge烧写flash时需要自己生成一个jtage birdge文件。jtage bridge 工程的目的是为了打通JTAG与flash的连接。 (1)打开IPM (2)选择Memory Controllers --> Jtag spi flash loader (3)随便命个名。可以考虑把fifo深度加大。 (4)在Deliverables界面根据自己的需要选择相应的demo,如果没有找到自己想用的器件就选择相近的生成之后自己修改器件 。 (5)生成IP之后,会在IP目录文件夹下生成一个example design,打开该工程。 这里需要说

- 专栏XL FPGA技术交流

- 1月前

- 719

- 0

- 0

AMD自适应计算加速平台之GTYP收发器误码率测试IBERT实验(6)

实验VIvado工程为“ibert_test”,目录中还有一个“ibert_ex”,是生成的测试工程。

- 专栏ALINX

- 1月前

- 1204

- 0

- 0